# МЕЖГОСУДАРСТВЕННОЕ ОБРАЗОВАТЕЛЬНОЕ УЧРЕЖДЕНИЕ ВЫСШЕГО ОБРАЗОВАНИЯ «БЕЛОРУССКО-РОССИЙСКИЙ УНИВЕРСИТЕТ»

Кафедра «Автоматизированные системы управления»

### АРХИТЕКТУРА ЭВМ

Методические рекомендации к лабораторным работам для студентов специальностей 6-05-0611-01 «Информационные системы и технологии» и 6-05-0612-03 «Системы управления информацией» очной и заочной форм обучения

УДК 004.2 ББК 32.973-02 A87

#### Рекомендовано к изданию учебно-методическим отделом Белорусско-Российского университета

Одобрено кафедрой «Автоматизированные системы управления» «7» марта 2025 г., протокол № 9

Составитель канд. физ.-мат. наук, доц. Ю. Д. Столяров

Рецензент канд. техн. наук, доц. С. К. Крутолевич

Методические рекомендации к лабораторным работам предназначены для студентов специальностей 6-05-0611-01 «Информационные системы и технологии» и 6-05-0612-03 «Системы управления информацией» очной и заочной форм обучения.

#### Учебное издание

#### АРХИТЕКТУРА ЭВМ

Ответственный за выпуск А. И. Якимов

Корректор А. А. Подошевко

Компьютерная верстка Н. П. Полевничая

Издатель и полиграфическое исполнение: Межгосударственное образовательное учреждение высшего образования «Белорусско-Российский университет». Свидетельство о государственной регистрации издателя, изготовителя, распространителя печатных изданий № 1/156 от 07.03.2019. Пр-т Мира, 43, 212022, г. Могилев.

© Белорусско-Российский университет, 2025

#### Содержание

| Введение                                                        | 4          |

|-----------------------------------------------------------------|------------|

| 1 Лабораторная работа № 1. Исследование принципа работы и       |            |

| составных частей ЭВМ                                            | 5          |

| 2 Лабораторная работа № 2. Исследование работы центрального     |            |

| процессора                                                      | 7          |

| 3 Лабораторная работа № 3. Исследование работы логических       |            |

| устройств                                                       | 10         |

| 4 Лабораторная работа № 4. Изучение работы элементов            |            |

| запоминающих устройств-тригеров                                 | 12         |

| 5 Лабораторная работа № 5. Исследование работы счетчиков        |            |

| различного типа                                                 | 15         |

| 6 Лабораторная работа № 6. Исследование работы различных        |            |

| регистров                                                       | 17         |

| 7 Лабораторная работа № 7. Исследование работы преобразователей |            |

| кода                                                            | 19         |

| 8 Лабораторная работа № 8. Исследование работы сумматоров       |            |

|                                                                 |            |

| Список литературы                                               | <i>2</i> 3 |

#### Введение

Целью преподавания дисциплины «Архитектура ЭВМ» является обучение студентов принципам построения и организации ЭВМ в составе автоматизированных систем обработки информации, изучение работы отдельных узлов ЭВМ, формирование устойчивых навыков по их применению.

Цель методических рекомендаций – помочь студентам в подготовке к выполнению лабораторных работ по дисциплине.

### 1 Лабораторная работа № 1. Исследование принципа работы и составных частей ЭВМ

Цель работы: ознакомиться с назначением и составными частями ЭВМ.

#### Порядок выполнения работы

- 1 Изучить основные теоретические положения.

- 2 Оформить отчет, содержащий краткие описания основных узлов ЭВМ.

#### Основные теоретические положения

**Архитектура ЭВМ.** Под архитектурой ЭВМ можно понимать ту совокупность их характеристик, которая необходима пользователю: основные устройства и блоки ЭВМ, структура связей между ними.

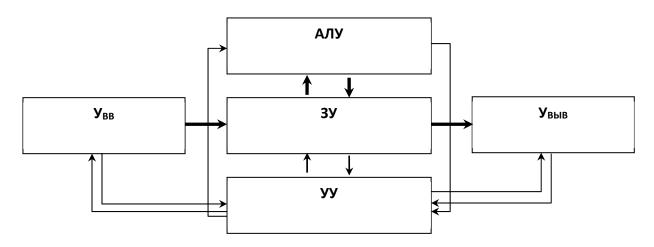

Основы учения об архитектуре вычислительных машин заложил выдающийся американский математик Джон фон Нейман, высказав идею принципиально новой ЭВМ. Нейман выдвинул основополагающие принципы логического устройства ЭВМ и его структуру (рисунок 1.1). ЭВМ имеет процессор, основную память и внешние устройства.

${\rm ЛУ}-{\rm арифметико}$ -логическое устройство;  ${\rm 3Y}-{\rm запоминающее}$  устройство;  ${\rm УУ}-{\rm устройство}$  управления;  ${\rm УВВ}-{\rm устройство}$  ввода;  ${\rm УВЫВ}-{\rm устройство}$  вывода

Рисунок 1.1 – Классическая структура ЭВМ А

**Арифметико-логическое устройство (АЛУ)** обеспечивает выполнение процедур преобразования данных.

**Устройство управления (УУ)** обеспечивает управление процессом обработки данных. УУ выбирает команды программы из основной памяти, интерпретирует тип команды и запускает нужную схему АЛУ.

Запоминающие устройства процессора обеспечивают промежуточное хранение обрабатываемых процессором данных. Основная память ЭВМ включает оперативную и постоянную память.

*Оперативная память* – устройство, обеспечивающее временное хранение команд и данных в процессе выполнения программы.

**Постоянная память** – устройство, обеспечивающее постоянное хранение и возможность считывания критически важной для функционирования ЭВМ информации.

**Внешние устройства** — устройства, обеспечивающие ввод и вывод данных из основных устройств ЭВМ (устройства ввода-вывода) и долговременное хранение информации, не обрабатываемой процессором в данный момент времени (внешние запоминающие устройства).

В одной ЭВМ может использоваться от единиц до нескольких сотен внешних устройств разных типов. Состав устройств ввода-вывода, как правило, переменный и определяется составом задач, решаемых на конкретной ЭВМ.

Производительность и эффективность использования ЭВМ определяется не только составом и характеристиками ее устройств, но также и способом организации их совместной работы. Связь между устройствами ЭВМ осуществляется с помощью сопряжений, которые в вычислительной технике называются интерфейсами.

Интерфейс представляет собой совокупность стандартизированных аппаратных и программных средств, обеспечивающих обмен информацией между устройствами. В основе построения интерфейса лежат унификация и стандартизация (использование единых способов кодирования данных, форматов данных, стандартизация соединительных элементов — разъемов и т. д.). Наличие стандартных интерфейсов позволяет унифицировать передачу информации между устройствами независимо от их особенностей.

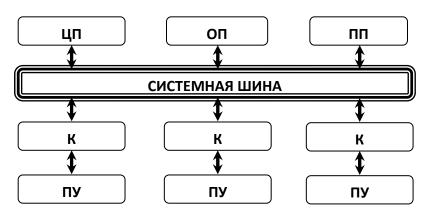

В ПК используется структура с шинным интерфейсом (рисунок 1.2). Разрядность шины определяет число битов информации, которые могут передаваться по шине одновременно. Количество адресных линий определяет, какой объем оперативной памяти (ОП) может быть адресован.

$\Pi$  — центральный процессор;  $\Pi$  — оперативная память;  $\Pi$  — постоянная память;  $\Pi$  — постоянная память;  $\Pi$  — периферийное устройство

#### Рисунок 1.2 – Шины ПК

Модульность структуры ЭВМ требует стандартизации и унификации оборудования, номенклатуры технических и программных средств, средств сопряжения — интерфейсов, конструктивных решений, унификации типовых элементов замены, элементной базы и нормативно-технической документации.

Детализацией архитектурного и структурного построения ЭВМ занимаются различные категории специалистов вычислительной техники.

Пользователя ЭВМ интересуют обычно более общие вопросы, касающиеся его взаимодействия с ЭВМ (человеко-машинного интерфейса), начиная со следующих групп характеристик ЭВМ, определяющих ее структуру:

- технические и эксплуатационные характеристики ЭВМ (быстродействие и производительность, показатели надежности, достоверности, точности, емкость оперативной и внешней памяти, габаритные размеры, стоимость технических и программных средств, особенности эксплуатации и др.);

- характеристики и состав функциональных модулей базовой конфигурации ЭВМ;

- возможность расширения состава технических и программных средств;

- возможность изменения структуры;

- состав ПО ЭВМ и сервисных услуг (ОС или среда, пакеты прикладных программ, средства автоматизации программирования).

#### Вопросы для контроля

- 1 Что такое архитектура ЭВМ?

- 2 Из каких основных узлов состоит ЭВМ?

- 3 Назначение основных устройств ЭВМ.

- 4 Какие преимущества имеет магистральная структура ЭВМ?

### 2 Лабораторная работа № 2. Исследование работы центрального процессора

**Цель работы**: ознакомиться с принципами работы основного узла процессора арифметико-логического устройства (АЛУ), собрать одноразрядное АЛУ, собрать АЛУ на микросхеме и исследовать их работу.

#### Порядок выполнения работы

- 1 Изучить основные теоретические положения

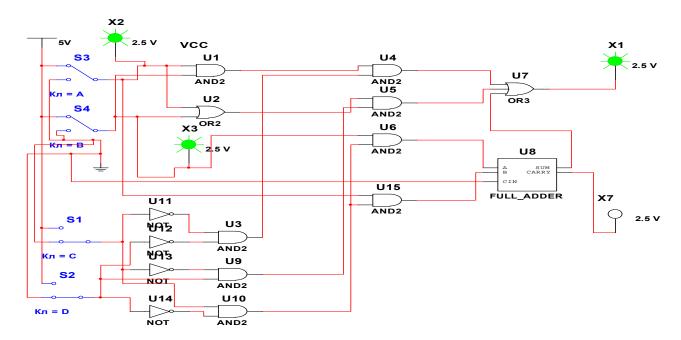

- 2 Собрать схему одноразрядного АЛУ из набора логических элементов и проверить его работу (рисунок 2.1).

- 3 Выполнить несколько операций АЛУ на микросхеме по указанию преподавателя.

- 4 Оформить отчет, содержащий краткие описания работы простейшего АЛУ и АЛУ на микросхеме.

#### Основные теоретические положения

АЛУ является основным исполнительным узлом процессора, предназначенным для выполнения логических и арифметических операций. Для наглядности рассмотрим вначале одноразрядное АЛУ (см. рисунок 2.1). В одноразрядном

АЛУ все действия выполняются параллельно, а выводится результат, заданный рассматриваемым режимом. В многоразрядном АЛУ на микросхеме выполняется только та операция, которая задана таблицей и в ней учитывается возможность переносов из младших разрядов.

Рисунок 2.1 – Одноразрядное АЛУ

Ключи S3и S4 используются для ввода информации, ключи S1и S2 задают режим работы (00 – логическое умножение И; 01 – логическое сложение ИЛИ; 10 – арифметическое сложение). X1 – результат логических операций; X1 и X7 – арифметическая сумма чисел и перенос в старший разряд. Подаем различные комбинации информационных сигналов. Полученные результаты следует занести в таблицу истинности.

АЛУ простейшего типа дает возможность понять действия при выполнении логических и арифметических операций. Данное устройство в зависимости от выбранного режима выполняет поочередно различные операции. В сложных ЭВМ для ускорения работы используются одновременно несколько АЛУ, каждое из которых выполняет только одну операцию. Это дает возможность сразу обрабатывать отдельные независимые участки программ, что приводит к ускорению вычислений. Вторая часть работы дает возможность ознакомиться с обработкой многоразрядных чисел. Набор входных данных производится в двоичном коде, как и в обычной ЭВМ, но для лучшего усвоения материала предусмотрена индикация в привычном десятичном коде.

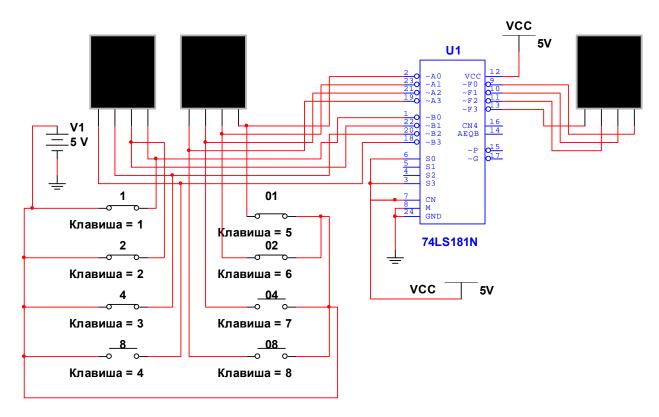

Исследовать работу устройства на микросхеме 74181 (рисунок 2.2). Подавая на входы A и B различные комбинации двоичных 4-разрядных чисел и задавая режимы работы с помощью входов S0...S3 через переключатели, получить результаты операций на выходах F. Установить соответствующие уровни сигналов на остальных выводах микросхем. Выбрать режим арифметических операций без входного переноса (рисунок 2.3).

Рисунок 2.2 – АЛУ на микросхеме

|    |    |    |    | M=1                                 | М=0 (арифмети                        | ческие операции)                        |

|----|----|----|----|-------------------------------------|--------------------------------------|-----------------------------------------|

| S3 | S2 | S1 | S0 | (логичес-<br>кие опера-<br>ции)     | CN=1 (входной перенос отсутствует)   | CN=0                                    |

| 0  | 0  | 0  | 0  | $\overline{A}$                      | A                                    | A+1                                     |

| 0  | 0  | 0  | 1  | $\overline{A \vee B}$               | $A \vee B$                           | $(A \lor B)+1$                          |

| 0  | 0  | 1  | 0  | $\overline{A} \wedge B$             | $A \vee \overline{B}$                | $(A \vee \overline{B})+1$               |

| 0  | 0  | 1  | 1  | 0                                   | -1                                   | 0                                       |

| 0  | 1  | 0  | 0  | $\overline{A \wedge B}$             | $A+A \wedge \overline{B}$            | $(A+A\wedge \overline{B})+I$            |

| 0  | 1  | 0  | 1  | $\overline{B}$                      | $(A \vee B) + A \wedge \overline{B}$ | $(A \lor B) + A \land \overline{B} + I$ |

| 0  | 1  | 1  | 0  | $A \ominus B$                       | A-B-1                                | A-B                                     |

| 0  | 1  | 1  | 1  | $A \wedge \overline{B}$             | $A \wedge \overline{B} - I$          | $A \wedge \overline{B}$                 |

| 1  | 0  | 0  | 0  | $\overline{A} \vee B$               | $A+A \wedge B$                       | $A+A \wedge B+1$                        |

| 1  | 0  | 0  | 1  | $\overline{A \ominus \overline{B}}$ | A+B                                  | A+B+1                                   |

| 1  | 0  | 1  | 0  | В                                   | $(A \lor \overline{B}) + A \land B$  | $(A \lor \overline{B}) + A \land B + I$ |

| 1  | 0  | 1  | 1  | A∧B                                 | $A \wedge B-I$                       | $A \wedge B$                            |

| 1  | 1  | 0  | 0  | 1                                   | A+A                                  | A+A+1                                   |

| 1  | 1  | 0  | 1  | $A \vee \overline{B}$               | $(A \lor B) + A$                     | $(A \lor B) + A + I$                    |

| 1  | 1  | 1  | 0  | A∨B                                 | $(A \vee \overline{B}) + A$          | $(A \vee \overline{B}) + A + 1$         |

| 1  | 1  | 1  | 1  | A                                   | A-I                                  | A                                       |

Рисунок 2.3 – Режимы арифметических операций АЛУ

- 1 Какие операции выполняет рассматриваемое АЛУ?

- 2 Чем отличается выполнение логических и арифметических операций?

- 3 Как влияет сигнал переноса из предыдущего разряда на окончательный результат?

- 4 Чем отличается выполнение логических и арифметических операций?

### 3 Лабораторная работа № 3. Исследование работы логических устройств

**Цель работы**: изучить основные логические элементы, используемые для создания узлов ЭВМ.

#### Порядок выполнения работы

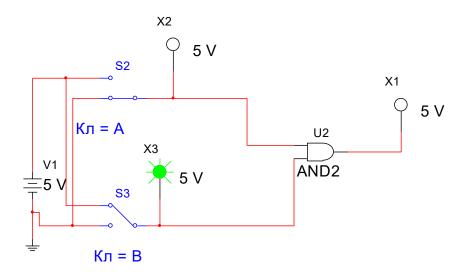

- 1 Собрать схему, указанную на рисунке 3.2.

- 2 Исследовать работу схемы.

- 3 Заполнить таблицу 3.1.

- 4 Оформить отчет. Отчет должен содержать подключение элементов, указанных в таблице 3.1, и таблицы истинности.

#### Основные теоретические положения

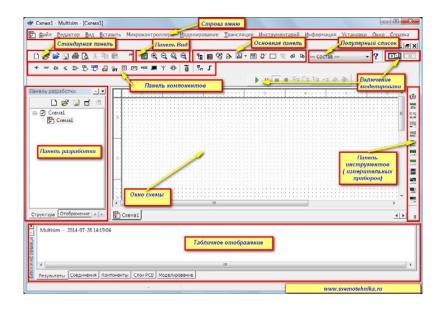

Логические элементы являются основными устройствами, используемыми для создания узлов ЭВМ. Зная назначение и принцип их работы, возможно создание и правильная эксплуатация ЭВМ. Изучение их работы проводится с использованием программного обеспечения Multisim 12.0.

Начнем с изучения интерфейса программы. Это программное обеспечение используется для исследования работы всех основных устройств ЭВМ. Основные функциональные панели программы показаны на рисунке 3.1. Использование программного продукта Multisim 12.0 позволяет смоделировать как отдельные логические элементы, так и сложные электронные компоненты вычислительных устройств. Для этого в программе предусмотрены возможности создания и исследования основных узлов ЭВМ.

Прохождение сигналов в различных узлах устройств может контролироваться с помощью генераторов сигналов и осциллографов. Изменяя параметры входных сигналов, можно выбрать оптимальные режимы работы исследуемых электронных узлов. Используемая программа позволяет проводить исследование работы как отдельных элементов ЭВМ, так и блоков, составленных из этих элементов. Изменяя входные параметры, можно визуально просмотреть с помощью осциллографа форму сигналов в любом месте ЭВМ. Использование компьютерных программ дает возможность провести предварительные исследования с це-

лью оптимизации затрат на изготовление конкретных физических устройств. Таким образом, вначале производим разработку виртуальных устройств и исследуем их работу, что дает значительную экономию материальных средств.

Рисунок 3.1 — Интерфейс программы Multisim 12.0

Рисунок 3.2 – Образец подключения элемента И

Таблица 3.1 – Таблица истинности логических элементов

| X1 | X2 | AND | NAND | OR | NOR | NOT | XOR |

|----|----|-----|------|----|-----|-----|-----|

| 0  | 1  |     |      |    |     |     |     |

| 1  | 0  |     |      |    |     |     |     |

| 0  | 0  |     |      |    |     |     |     |

| 1  | 1  |     |      |    |     |     |     |

С помощью панели компонентов осуществляется доступ к базе компонентов. При нажатии на любую из выбранных пиктограмм компонентов схем откры-

вается окно *Выбор компонента* (см. рисунок 3.1). В левой части окна осуществляется выбор необходимого компонента. Вся база данных компонентов разделена на разделы (пассивные элементы, диоды, транзисторы, микросхемы и т. д.), а разделы — на семейства (например, логические схемы — это схемы различных типов). Также в окне *Выбор компонента* можно посмотреть обозначение выбранного компонента, описание его функции, выбрать тип корпуса.

Выбрав необходимые компоненты узлов, объединяем их с помощью соединительных линий. Цвет линий для удобства выбираем различный, чтобы можно было проверить правильность сборки схемы. Затем подключаем различные приборы и индикаторы и проводим исследования работы схем в различных режимах.

Исследовать элементы И(AND), ИЛИ(OR), НЕ(NOT), И-E(NAND), ИЛИ-НЕ(NOR) и исключающее ИЛИ (XOR), заполнить таблицу 3.1.

#### Вопросы для контроля

- 1 Назначение логических элементов.

- 2 Типы логических элементов.

- 3 Принцип их работы.

- 4 Взаимозаменяемость логических элементов.

### 4 Лабораторная работа № 4. Изучение работы элементов запоминающих устройств (триггеров)

Цель работы: изучить принцип работы триггеров в различных режимах.

#### Порядок выполнения работы

- 1 Исследовать работу асинхронных триггеров.

- 2 Преобразовать асинхронные триггеры в синхронные.

- 3 Изучить работу ЈК- и D-триггеров.

- 4 Изучить работу Т-триггеров.

- 5 Оформить отчет, содержащий схемы исследований.

#### Основные теоретические положения

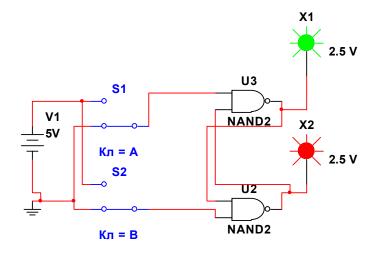

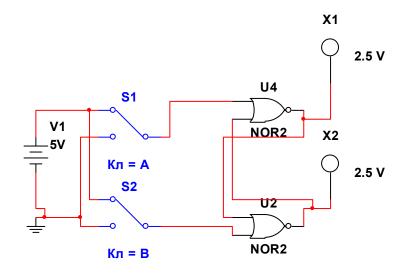

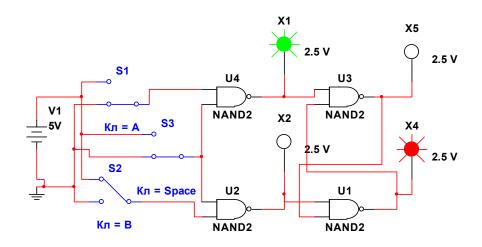

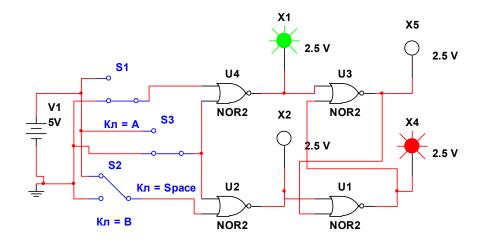

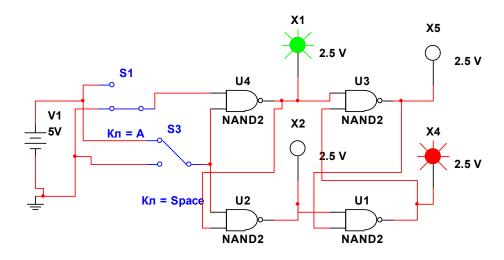

Основой запоминающих элементов и ЭВМ являются различные типы триггеров. Изучим их работу. Вначале исследуем асинхронные триггеры на элементах И-НЕ и ИЛИ-НЕ (рисунки 4.1 и 4.2), для этого на входы через переключатели подадим возможные комбинации двоичных сигналов и зарегистрируем выходные сигналы. Полученные результаты внести в таблицы истинности.

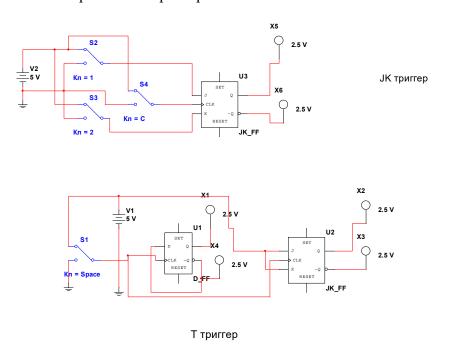

Затем преобразовать асинхронные триггеры в синхронные и добавить переключатель для входа сигнала синхронизации С. Произвести аналогичные рассмотренным выше исследования. Исследовать D- и JK-триггеры. Дальше исследовать Т-триггер, используя D- и JK-триггеры (рисунки 4.3–4.6).

Рисунок 4.1 – Асинхронный триггер на элементах И-НЕ

Рисунок 4.2 – Асинхронный триггер на элементах ИЛИ-НЕ

Рисунок 4.3 – Синхронный триггер на элементах И-НЕ

Рисунок 4.4 – Синхронный триггер на элементах ИЛИ-НЕ

Рисунок 4.5 – Синхронный D-триггер

Рисунок 4.6 – Синхронные ЈК- и Т-триггеры

- 1 Назначение триггеров и их типы.

- 2 Асинхронные триггеры.

- 3 Синхронные триггеры.

- 4 JK-, D- и Т-триггеры.

## 5 Лабораторная работа № 5. Исследование работы счетчиков различного типа

Цель работы: исследовать различные типы счетчиков.

#### Порядок выполнения работы

- 1 Собрать и исследовать схемы (рисунки 5.1–5.4).

- 2 Оформить отчет, содержащий схемы исследований на отдельных триггерах и микросхемах.

#### Основные теоретические положения

В ЭВМ счетчики используются для подсчета шагов программы, различных элементов временной задержки и т. д. Собрать схемы суммирующих и вычитающих счетчиков на D- и JK-триггерах, используя приведенные схемы, составить таблицы двоичных сигналов на выходах триггеров в зависимости от количества входных импульсов (см. рисунки 5.1 и 5.2).

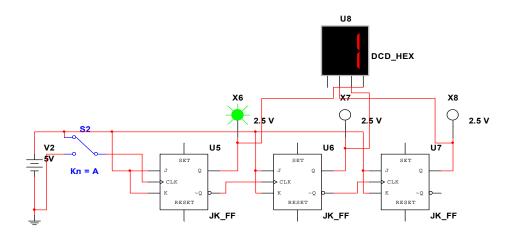

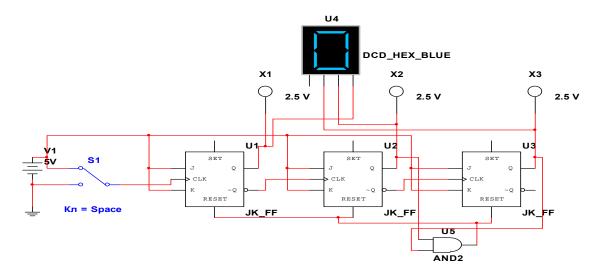

Рисунок 5.1 – Суммирующий счетчик на ЈК-триггерах

При сборке счетчиков свободные выводы не должны ни к чему подключаться. Для наглядности используется цифровой десятичный индикатор, а также индикация выходных сигналов с помощью светодиодов.

Преобразовать двоичный счетчик на ЈК-триггерах в счетчик с произвольным коэффициентом счета (см. рисунок 5.2).

Рисунок 5.2 – Суммирующий счетчик на JK-триггерах с произвольным коэффициентом счета

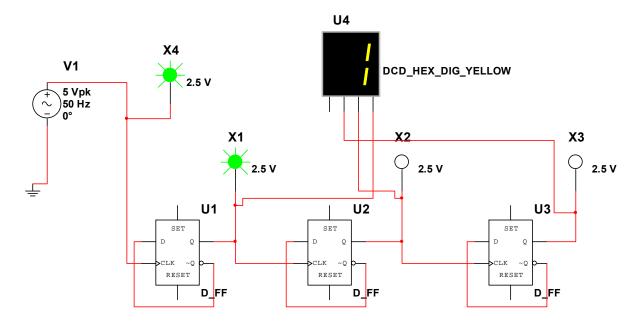

Рисунок 5.3 – Вычитающий счетчик на D-триггерах

Коэффициент счета задается с помощью элемента И, на входы которого поданы соответствующие двоичные сигналы. Выходной сигнал используется для сброса счетчика в нулевое состояние при достижении нужного коэффициента пересчета.

Собрать вычитающий счетчик на D-триггерах (см. рисунок 5.3).

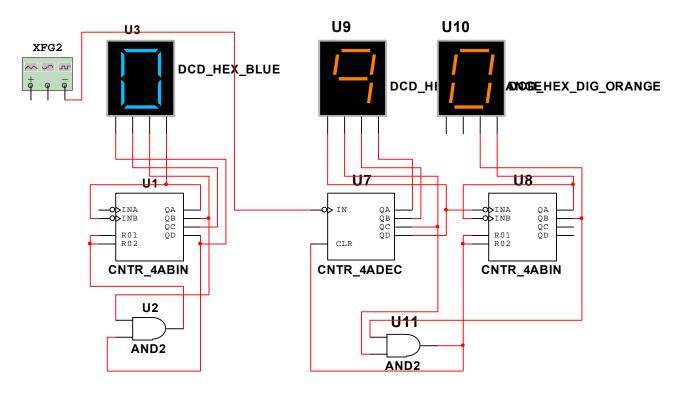

Собрать счетчики на микросхемах, указанных на логических элементах (см. рисунок 5.4). В качестве индикаторов использовать цифровые индикаторы с дешифратором. В качестве источника сигналов применить генератор прямоугольных импульсов.

Рисунок 5.4 – Счетчик на 10 и 24 на микросхемах

- 1 Как работает суммирующий счетчик на ЈК-триггерах?

- 2 Объяснить принцип работы счетчика с произвольным коэффициентом счета.

- 3 Как работает вычитающий счетчик на D-триггерах?

- 4 Как работает счетчик на микросхемах?

## 6 Лабораторная работа № 6. Исследование работы различных регистров

Цель работы: изучить назначение и типы регистров ЭВМ.

#### Порядок выполнения работы

- 1 Исследовать последовательный и кольцевой регистры.

- 2 Изучить работу параллельного регистра.

- 3 Исследовать реверсивный регистр.

- 4 Исследовать регистр на микросхеме.

- 5 Продемонстрировать работу преподавателю, оформить отчет с результатами исследований.

#### Основные теоретические положения

Регистры — это устройства, предназначенные для хранения и обработки информации. В зависимости от назначения они бывают последовательные, параллельные и комбинированные. На основании предложенной схемы собрать *четы-рехразрядный* последовательный регистр (рисунок 6.1).

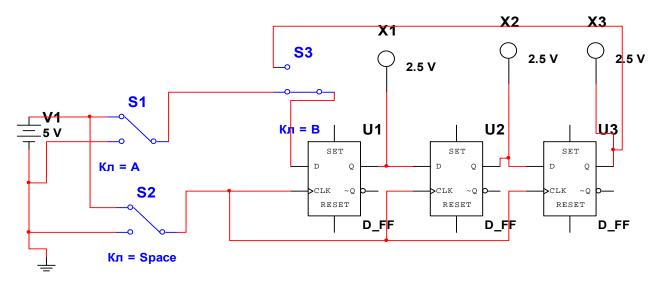

Рисунок 6.1 – Сдвиговый последовательный регистр

Регистр собран на D-триггерах. Запись информации производится с помощью ключа S2, при этом ключ S2 находится в нижнем положении, а входной код определяется положением ключа S1. Ключ S2 разомкнут. Для того чтобы информация не пропала, она может быть закольцована после записи соединением выхода последнего триггера со входом первого через ключ S2 (ключ S1 разомкнут) и многократно считываться без потерь с помощью ключа S2. Исследовать четырехразрядный параллельный регистр.

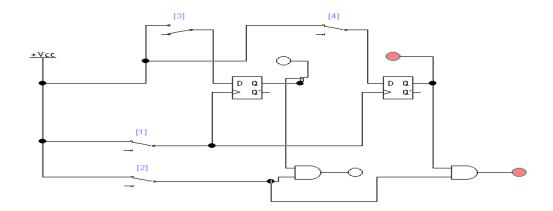

Схема двухразрядного параллельного регистра (рисунок 6.2). предусматривает ввод информации в регистр с помощью ключей 2 и 4 и узла записи — ключа 1. Считывание информации производится ключом 2 с помощью схем И. Преобразовать этот регистр в *четырехразрядный*.

Рисунок 6.2 – Двухразрядный параллельный регистр

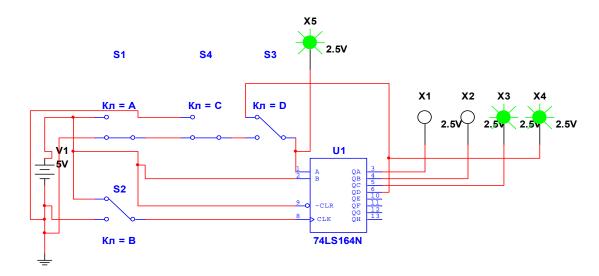

Собрать последовательный сдвиговый регистр на микросхеме 74164 (рисунок 6.3). Подать на вход сигналы с помощью ключей A и C, произвести запись и чтение информации из него (ключ В).

Рисунок 6.3 – Последовательный регистр на микросхеме

Преобразовать этот регистр в кольцевой, используя ключ D, и проверить его работу.

#### Вопросы для контроля

- 1 Как работает последовательный регистр?

- 2 Как работает кольцевой регистр?

- 3 Как работает параллельный регистр?

- 4 Как осуществляется сдвиг информации в регистре вправо и влево?

- 5 Как работает последовательный регистр на микросхеме?

### 7 Лабораторная работа № 7. Исследование работы преобразователей кода

**Цель работы**: изучить принципы преобразования двоичных кодов в ЭВМ при проведении различных операций.

#### Порядок выполнения работы

- 1 Согласно таблицам истинности разработать конкретные электрические схемы.

- 2 Продемонстрировать работу преподавателю.

- 3 В отчете представить разработанные схемы.

#### Основные теоретические положения

Порты ввода/вывода могут передавать информацию в прямом и обратном кодах. Разработать устройство, позволяющее передавать на выход сигнал X в обратном или дополнительном кодах в зависимости от входного сигнала: Y = 1 -в обратном коде, y = 0 -в дополнительном. Число разрядов - 4. Использовать таблицу истинности (таблица 7.1).

| X | Y | Z |

|---|---|---|

| 0 | 1 | 1 |

| 1 | 1 | 0 |

| 0 | 0 | 0 |

| 1 | 0 | 1 |

Таблица 7.1 – Таблица истинности преобразователя кода

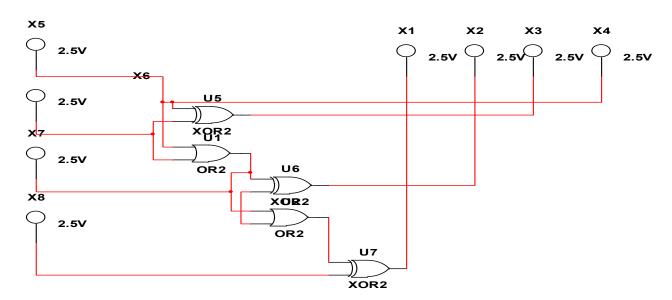

Собрать схему, преобразующую входной сигнал в дополнительный код. Обратный код получается инверсией прямого кода. Правила образования дополнительного кода из прямого могут быть выражены соотношением  $Yi = (x1 + x2 + x2 + ... + x_{i-1}) \otimes x_i$ . Отсюда следует, что x1 = y1, т. е. младшие разряды чисел в прямом и дополнительном кодах совпадают. Схема приведена на рисунке 7.1.

При создании преобразователя кодов желательно собрать одну универсальную схему, которая в зависимости от задания выдавала бы тот или иной код. Для этого надо предусмотреть набор входных данных с помощью ключей. Для вывода обратного кода предусмотреть отдельные индикаторы. Переключение в различные режимы осуществлять тоже с помощью дополнительных ключей. Индикация состояний производится с помощью светодиодов.

Рисунок 7.1 – Схема преобразователя кодов

- 1 Что такое прямой, обратный и дополнительный коды?

- 2 Как работает разработанная схема?

- 3 Какие элементы используются в схеме и почему?

#### 8 Лабораторная работа № 8. Исследование работы сумматоров

**Цель работы**: изучить работу сумматоров, использующихся для арифметического сложения двоичных чисел в ЭВМ.

#### Порядок выполнения работы

- 1 Собрать электрические схемы (рисунки 8.1 и 8.2).

- 2 Продемонстрировать работу схем преподавателю.

- 3 Составить отчет. В отчете представить схемы и результаты.

#### Основные теоретические положения

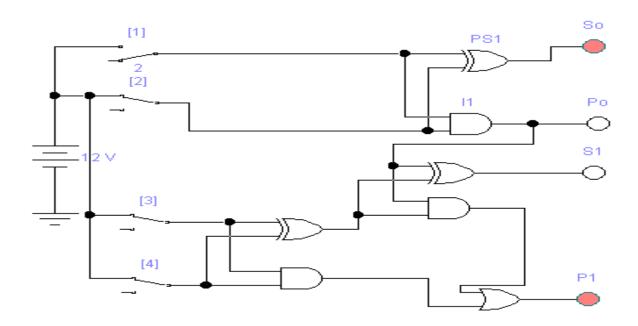

Для сложения чисел используются специальные устройства, называемые сумматорами. Для сложения младших разрядов используется полусумматор и возможен перенос в старший разряд, в котором будут складываться три разряда и здесь необходим полный сумматор (см. рисунок 8.1). Результат сложения младших разрядов фиксируется индикатором So, возможный перенос из младшего разряда может быть зафиксирован как Po. Заполнить таблицу 8.1, собрав схему.

Рисунок 8.1 – Полный сумматор

Таблица 8.1 – Таблица полусумматора

| al | в1 | So | Po |

|----|----|----|----|

|    |    |    |    |

Затем исследуем работу двухразрядного сумматора. Он состоит из полусумматора (PS1 и II) для сложения двух младших разрядов (двух чисел) и полного сумматора для сложения старших разрядов и возможного переноса из младшего разряда (трех чисел). Так как максимальное десятичное число, представленное двумя двоичными разрядами, равно 2, то произведем сложение различных чисел от 1 до 2. Здесь So — сумма младших разрядов, S1 — сумма старших разрядов, P1 — возможный перенос из старшего разряда суммы. Первое число a2a1, второе в2в1, переключатели 2 и 4 соответствуют a2 и в2. Заполним таблицу 8.2.

Таблица 8.2 – Таблица полного сумматора

| a2 | a1 | в2 | в1 | P1 | S1 | So |

|----|----|----|----|----|----|----|

|    |    |    |    |    |    |    |

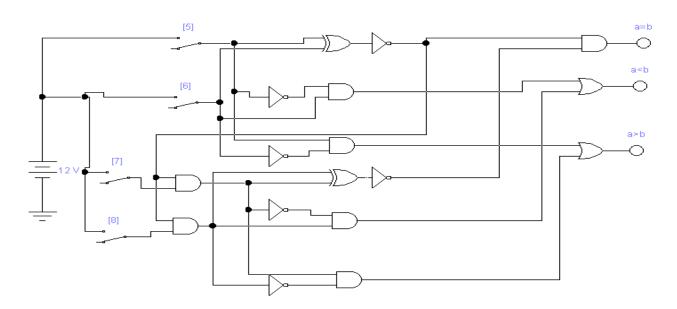

На рисунке 8.2 приведена схема для сравнения двух двухразрядных чисел. Переключатели 5 и 6 соответствуют старшим разрядам чисел, а 7 и 8 — младшим. Собрать схему. Подать различные двоичные числа на входы и заполнить таблицу 8.3. Объяснить работу устройства. Сначала сравниваются старшие разряды чисел и фиксируется результат, при их равенстве происходит сравнение младших разрядов чисел и результат выводится на те же индикаторы.

Рисунок 8.2 – Схема сравнения двухразрядных чисел

Таблица 8.3 – Таблица сравнения двух чисел

| a2 | a1 | в2 | в1 | a = B | $a \le B$ | a > B |

|----|----|----|----|-------|-----------|-------|

|    |    |    |    |       |           |       |

- 1 Как работает одноразрядный сумматор?

- 2 Как работает двухразрядный сумматор?

- 3 Как работает схема сравнения одноразрядных чисел?

- 4 Как работает схема сравнения многоразрядных чисел?

#### Список литературы

- 1 **Бройдо, В. Л.** Вычислительные системы, сети и телекоммуникации : учебник / В. Л. Бройдо. 4-е изд. СПБ.: Питер, 2012. 560 с.: ил.

- 2 **Партыка, Т.** Л. Вычислительная техника : учеб. пособие / Т. Л. Партыка, И. И. Попов. 2-е изд., перераб. и доп. М. : ФОРУМ ; ИНФРА-М, 2017. 445 с. : ил.